硬件描述语言verilog,硬件描述语言的魅力与运用

时间:2024-09-29 来源:网络 人气:

深入浅出Verilog:硬件描述语言的魅力与运用

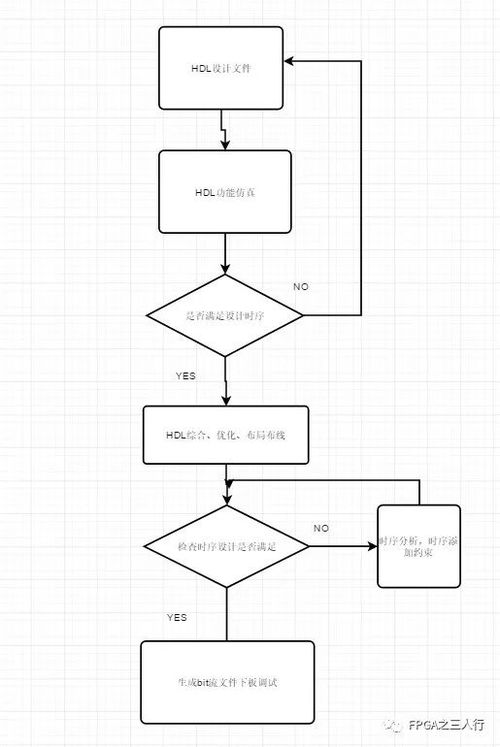

在数字电路设计领域,硬件描述语言(HDL)已成为不可或缺的工具。Verilog作为其中一种主流的HDL,以其简洁的语法和强大的功能,在FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)的设计中发挥着重要作用。本文将深入浅出地介绍Verilog的基本概念、语法结构、设计方法和应用场景。

Verilog是一种硬件描述语言,用于描述数字系统的结构和行为。它允许设计者以文本形式表达电路的功能,从而实现电路的仿真、综合和测试。Verilog最初由Gateway Design Automation开发,后被Cadence Design Systems收购,并最终成为IEEE标准(IEEE 1364)的一部分。

Verilog的语法结构类似于高级编程语言,包括模块、端口、数据类型、连续赋值语句、过程块等。以下是一些基本的语法元素:

模块(module):定义了Verilog设计的单元,类似于C语言中的函数。

端口(port):模块的输入和输出接口,用于与其他模块进行交互。

数据类型:包括整数、实数、逻辑等,用于定义变量的类型。

连续赋值语句(always块):描述了模块的行为,类似于C语言中的函数体。

过程块(initial块和always块):用于初始化和时序控制。

Verilog设计方法主要包括以下几种:

行为级设计:描述电路的功能,不涉及具体的电路结构。

结构级设计:描述电路的结构,包括模块的连接和组合逻辑。

门级设计:描述电路的门级结构,包括逻辑门和触发器。

在实际应用中,设计者可以根据需求选择合适的设计方法。例如,在FPGA设计中,行为级和结构级设计较为常见;而在ASIC设计中,门级设计更为常用。

在仿真过程中,设计者可以使用测试向量(testbench)来模拟输入信号,观察输出信号的变化,从而验证设计的正确性。以下是一个简单的测试向量示例:

```verilog

initial begin

// 初始化输入信号

clk = 0;

reset = 1;

10 reset = 0;

10 reset = 1;

// 生成时钟信号

forever 5 clk = ~clk;

Verilog在以下领域具有广泛的应用:

FPGA设计:Verilog是FPGA设计的主要语言,用于实现各种数字逻辑功能。

ASIC设计:Verilog可以用于ASIC设计,实现复杂的数字系统。

嵌入式系统:Verilog可以用于嵌入式系统设计,实现数字信号处理、通信等功能。

系统级仿真:Verilog可以用于系统级仿真,验证整个系统的功能和性能。

以下是一些Verilog学习资源:

Verilog数字系统设计教程

Verilog HDL设计与应用

在线教程和视频课程

开源代码和项目

Verilog作为一种强大的硬件描述语言,在数字电路设计领域具有广泛的应用。通过学习Verilog,设计者可以高效地设计和验证数字系统,提高设计质量和效率。本文简要介绍了Verilog的基本概念、语法结构、设计方法和应用场景,希望对初学者有所帮助。

相关推荐

教程资讯

教程资讯排行