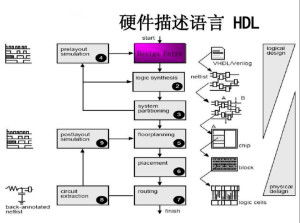

硬件描述语言程序,深入浅出硬件描述语言程序设计——Verilog入门指南

时间:2024-09-24 来源:网络 人气:

深入浅出硬件描述语言程序设计——Verilog入门指南

随着电子技术的飞速发展,硬件描述语言(HDL)已成为现代电子系统设计的重要工具。Verilog作为HDL的一种,因其简洁的语法和强大的功能,在FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)设计中得到了广泛应用。本文将为您深入浅出地介绍Verilog程序设计的基础知识,帮助您快速入门。

一、Verilog简介

Verilog是一种硬件描述语言,用于描述电子系统的行为和结构。它允许设计者以文本形式描述电子系统的功能,并通过仿真和综合工具将设计转换为实际的硬件电路。Verilog不仅适用于FPGA设计,也广泛应用于ASIC开发中。

二、Verilog基本语法

Verilog的语法结构对于初学者来说可能有些陌生,但一旦掌握,它将极大地提高设计效率。以下是Verilog编程的基础元素:

1. 模块定义

模块是Verilog程序的基本单位,它定义了电路的一部分或全部功能。模块定义通常包含以下内容:

模块名称

端口定义

信号类型声明

逻辑功能定义

2. 运算符与表达式

Verilog支持多种运算符,包括算术运算符、逻辑运算符、位运算符和关系运算符。运算符用于对信号进行数学和逻辑运算。

3. 语句

Verilog语句用于描述数字电路的行为和功能,包括赋值语句、块语句、条件语句和循环语句等。

三、Verilog程序框架

Verilog程序框架通常包含以下部分:

1. 模块级

模块级是Verilog程序的最高层次,它定义了电路的整体功能。模块级通常包含以下内容:

模块定义

端口定义

内部信号定义

逻辑功能实现

2. 实例级

实例级是模块级的具体实现,它将模块应用于电路中。实例级通常包含以下内容:

模块实例化

端口连接

内部信号连接

四、Verilog编程规范

为了提高代码的可读性和可维护性,Verilog编程应遵循以下规范:

1. 命名规范

遵循一致的命名规范,例如使用驼峰命名法、下划线分隔等。

2. 代码格式

保持代码格式整齐,例如缩进、空格等。

3. 注释

添加必要的注释,解释代码的功能和实现方式。

五、总结

Verilog是一种功能强大的硬件描述语言,广泛应用于电子系统设计。通过本文的介绍,相信您已经对Verilog程序设计有了初步的了解。在实际应用中,不断学习和实践,您将能够熟练掌握Verilog编程,为电子系统设计贡献力量。

标签:硬件描述语言 Verilog FPGA ASIC 电子设计 编程规范相关推荐

教程资讯

教程资讯排行